# GaAs MMIC **Power Amplifier**

AM357039WM-00-R AM357039WM-SN-R

> December 2012 Rev0

#### **DESCRIPTION**

AMCOM's AM357039WM is a broadband GaAs MMIC Power Amplifier. It has a nominal CW performance of 21dB small signal gain, and 38.5dBm (7W) saturated output power over the 3.5 to 7GHz band. The MMIC is offered in both chip (-00-R) and package (-SN-R) forms. The AM357039WM-SN-R is in a ceramic package with a flange and straight RF and DC leads for drop-in assembly. Because of high DC power dissipation, good heat sinking is required, and the chip MMIC has to be mounted using eutectic soldering directly on a metal ridge. Both chip and package are RoHS compliant.

#### **FEATURES**

- Wide bandwidth from 3.5 to 7GHz

- 38.5dBm of saturated CW output power

- High gain, 21dB

- Input /Output matched to 50 Ohms

#### **APPLICATIONS**

- Commercial telecom transmission equipment

- Fixed microwave backhaul

- Commercial 2-way radio

# TYPICAL PERFORMANCE \* ( $V_{ds1.2} = 14V$ , $I_{dsa1} = 0.3A$ , $I_{dsa2} = 1.2A$ )

| Parameters                    | Minimum    | Typical ** | Maximum |

|-------------------------------|------------|------------|---------|

| Frequency                     | 4 – 6.5GHz | 3.5 – 7GHz |         |

| Small Signal Gain             |            | 21dB       | 26dB    |

| Gain Ripple                   |            | ± 3dB      | ± 5dB   |

| P <sub>1dB</sub>              | 35dBm      | 37dBm      |         |

| P <sub>3dB</sub>              | 36.5dBm    | 38.5dBm    |         |

| Efficiency @ P <sub>3dB</sub> |            | 24%        |         |

| Noise Figure                  |            | -          | 10dB    |

| IP3 @ 5GHz                    |            | TBD        |         |

| Input Return Loss             |            | 15dB       |         |

| Output Return Loss            |            | 5dB        |         |

| Thermal Resistance            |            | 5.2 °C/W   |         |

Email:

- 1- Specifications are subject to change without notice.

- 2- V<sub>as1,2</sub> should be adjusted to -0.85V approximately to get the specified currents, and will vary slightly from one unit

- 3- Measurements are done in CW mode.

December 2012, Preliminary

## **ABSOLUTE MAXIMUM RATING**

| Parameters                     | Symbol             | Rating          |

|--------------------------------|--------------------|-----------------|

| Drain source voltage           | V <sub>ds1,2</sub> | 16V             |

| Gate source voltage            | V <sub>gs1,2</sub> | -3V             |

| Drain source current           | I <sub>dsq1</sub>  | 0.375A          |

| Drain source current           | I <sub>dsq2</sub>  | 1.5A            |

| Continuous dissipation at 25°C | Pt                 | 38 W            |

| Channel temperature            | T <sub>ch</sub>    | 175°C           |

| Operating temperature          | T <sub>op</sub>    | -55°C to +85°C  |

| Storage temperature            | T <sub>sto</sub>   | -55°C to +135°C |

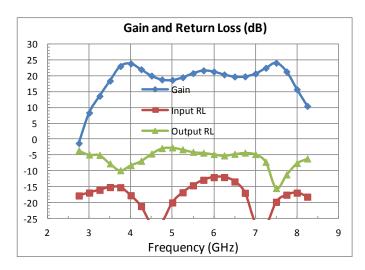

## **SMALL SIGNAL DATA\***

<sup>\*</sup> Data shown is for packaged version (SN-R) of the MMIC biased at  $V_{ds1,2}$  = 14V,  $I_{dsq1}$  = 0.3A,  $I_{dsq2}$  = 1.2A.

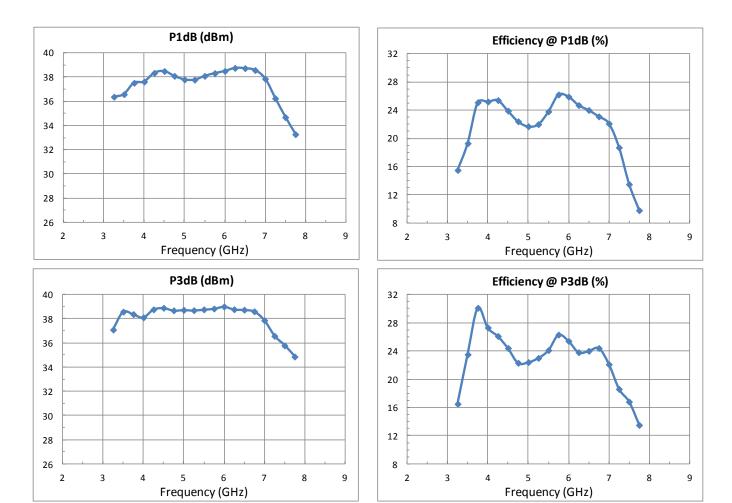

## **POWER DATA\***

<sup>\*</sup> Data shown is for packaged version (SN-R) of the MMIC biased at  $V_{ds1,2} = 14V$ ,  $I_{dsq1} = 0.3A$ ,  $I_{dsq2} = 1.2A$  and measured in CW mode.

December 2012, Preliminary

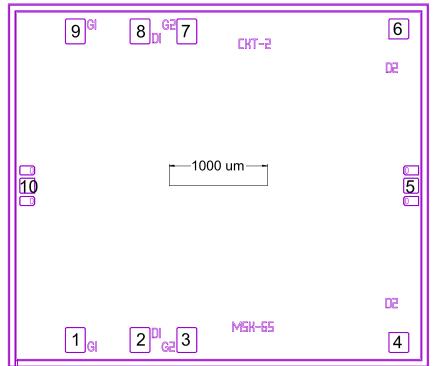

## **CHIP OUTLINE**

## Dim X\*Y: 4200X3600 um^2

| Pin No. | Function  | Bias   |

|---------|-----------|--------|

| 1       | $V_{gs1}$ | -0.85V |

| 2       | $V_{ds1}$ | +14V   |

| 3       | $V_{gs2}$ | -0.85V |

| 4       | $V_{ds2}$ | +14V   |

| 5       | RF out    | NA     |

| 6       | $V_{ds2}$ | +14V   |

| 7       | $V_{gs2}$ | -0.85V |

| 8       | $V_{ds1}$ | +14V   |

| 9       | $V_{gs1}$ | -0.85V |

| 10      | RF in     | NA     |

#### \*Notes:

- 1- It is necessary to connect drain biases  $V_{ds1,2}$  to both the upper and lower bonding pads.

- 2-  $V_{gs1,2}$  bias values are for reference only and will vary slightly from one unit to another. 3- When both first and second stages are pinched off ( $V_{gs1,2} < -2V$ ), there will still be a small current flowing in internal biasing circuitry.

## **CHIP TEST FIXTURE**

#### Notes:

- 1- Use epoxy to mount PCB, and eutectic soldering to mount chip.

- 2- C1=1uF, C2=1000pF, R1=50ohms, R2=10ohms, R3=5ohms.

- 3- All SMT Caps & Resistors are 0402 size.

- 4- Don't apply drain biases V<sub>ds1,2</sub> without proper negative voltages on corresponding gates.

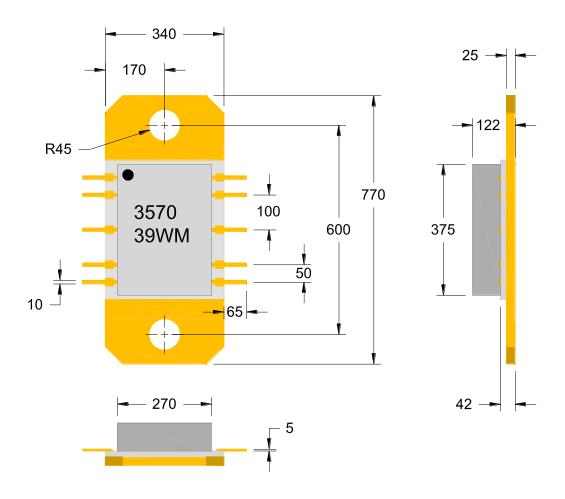

# **SN PACKAGE OUTLINE (Dimensions in mils)**

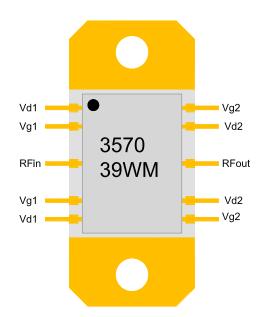

# **Pin Layout**

December 2012, Preliminary

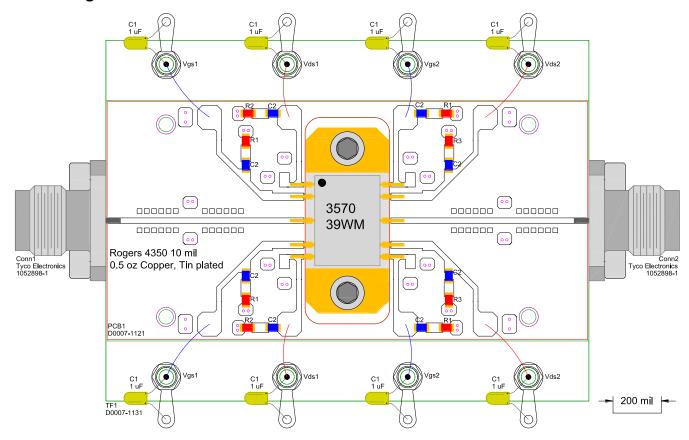

# **SN Package Test Fixture**

## Notes:

- 1- Use epoxy to mount PCB.

- 2- C1=1uF, C2=1000pF, R1=50ohms, R2=10ohms, R3=5ohms.

- 3- All SMT Caps & Resistors are 0603 size.

- 4- Don't apply drain biases V<sub>ds1,2</sub> without proper negative voltages on corresponding gates.